VHDL

| Paradigm | سلوكية |

|---|---|

| First appeared | 1980s |

| Typing discipline | شديد |

| Website | IEEE VASG |

VHDLهي اختصار لـVHSIC HDL وهي اختصار لـ Very High Speed Integrated Circuit Hardware Description Language وهي تعني لغة توصيف العتاد للدارات المتكاملة ذات السرعات المرتفعة جداً.

و لغة VHDL هي لغة برمجة قياسية صممت من قبل وزارة دفاع الولايات المتحدة حيث تستعمل في وصف، وتصميم، ومحاكاة دارات VHSIC. أصبحت منذ عام 1987 إحدى مقايس IEEE وتمت مراجعتها في عام 1997.

تتيح هذه اللغة توصيف التوازي و الترابط بالإضافة للتعبير المفصل والمباشر للزمن وتسمح ايضا بتوصيف الدارات التماثلية لكنها غالبا ما تستخدم في تصميم دارات FPGA.

VHDL مقتبسة من لغة Ada في المفهوم العام كالرموز و المصفوفات أحادية البعد وتركيب العبارات وبناءها وهي غير حساسة لحالة الأحرف وهناك الكثير من الميزات غير موجودة في لغة Ada كمجموعة من التعليمات البوليانية التي تتضمن NAND,NOR مثلا وتمثيل العمليات الشائعة في البنية التعاودية مباشرة. وتسمح VHDL بإدخال المصفوفات في اتجاهين تصاعدي وتنازلي لأن كلا الا صطلاحين يستخدم في الـ HardWare ،والنسخة المعدلة الأولى من الـ VHDL تتضمن مجال واسع من أنواع البانات كالنوع العددي(الصحيح والحقيقي)والمنطقي(البولياني والبتي)والنوع الحرفي والوقتومصفوفة من النوع البتي التي تسمى الشعاع البتي والمصفوفة من نوع المحارف التي تسمى الشعاع السلسلة.

لغة VHDL هي لغة متعددة وعامة تماماً وعلى الرغم من أنها تتطلب برنامج محاكاة لتشغيل كود البرنامج فإنه يمكنها أن تقرأ وتكتب ملفات على كمبيوتر مضيف ،إن VHDL تسمح بتوصيف النظام المتزامن (الأجزاء المقدمة بواسطة سلوك عملها مع بعضها البعض بنفس الوقت )وهي غير محببة كثيراً من لغات أخرى كلغة الـ Basic ، pascal ، c أو لغات التجميع التي تسمع على مستوى شيفرة الآلة بشكل متعاقب تعليمة واحدة كل مرة لكل بنيان . وعندما يترجم نموذج VHDL إلى بوابات وأسلاك التي تكون منظمة على جهاز منطقي قابل للبرمجة مثل FPGA أو CPLD والعتاد الفعلي يحدد من شيفرة VHDL المنفذة كما في بعض أشكال شريحة المعالج.

البداية:

في لغة VHDL كما في أي لغة برمجة عتادية أو برمجية كي تكون خبيراً فإن ذلك يتطلب دراسة وتمرين ،وإذا كان المستخدم يرغب بتعلم تشفيرRTL كتصميم دارات عتادية عن طريق VHDL فإن حزم التصميم و التركيب الموجودة كافية للتعلم.إن معرض البوابات التخطيطية يظهر للمستخدم تصاميم مركبة كالمخططات القابلة للانقياد ،والكثير من حزم التصميم FPGA تقدم طرق إدخال تصاميم بديلة مثل النسخ المؤقت لمخطط الحالة و الرسوم التخطيطية.وهذه الحزم تزودنا بقالب بدء مفيد لتشفير الأنواع الأساسية من التعليمات التكرارية و الدروس التي يتضمنها التي يتضمنها مفيدة ومساعدة . تقريباً جميع نسخ المحاكاة وتصميم FPGA تدعم كلا Verilog و VHDL تسمح للمستخدم بتعلم كلا اللغتين . بالإضافة إلى أن معظم التصاميم المستوردة نماذج من المكتبات وبعض التصاميم التي تتضمن عدة Architecture .

البنية الأساسية

- entity (كيان)، يحدد واجهة الترابط (المداخل و المخارج) فقط من دون تحديد الوظيفة.

- architecture (البنيان)، يحدد وظيفة الكيان و يتالف من قسمين تصريحي (declarative) و إيعازي (command).

طرق توصيف البنيان

- توصيف بنيوي structure

- التوصيف على مستويات عليا

- يستخدم بشكل اساسي لدى المحاكاة

- توصيف سلوكي behavior

- مناسب لعمليات التركيب synthesis

- المصمم يتحكم ببنية تصميمه.

باقات تصميم ومحاكاة مجانية لـ VHDL/Verilog:

| Vendor | Trial Software | License | Simulator | Synthesizer | RTL view | Gate view |

|---|---|---|---|---|---|---|

| Actel | Libero gold | one year free license | ModelSim Actel Edition | Synplify Actel Edition | No | yes** |

| Aldec | Active-HDL (Student Edition) | one year free license | Aldec (mixed language) Student | All Synthesis (interfaces) | yes | yes |

| Altera | Quartus II web edition | 6 months renewable free license | ModelSim Altera Edition | Altera Quartus II | yes | yes** |

| Lattice | ispLEVER Starter | 6 months renewable free license | Aldec Active-HDL Lattice Web Edition | Synopsys Synplify Lattice Edition | No | yes |

| Dolphin | none | free seduction license | SMASH | no | ? | ? |

| Mentor Graphics | none | 6 months renewable free license | ModelSim PE Student Edition | no | yes | no |

| Xilinx | ISE webpack | free license | ISE Simulator* | Xilinx XST | yes | yes** |

| Blue Pacific | BlueHDL | free license | BlueSim | ? | ? | ? |

| GHDL | GHDL | GPL | GHDL | no | via GTKWave | no |

* لو كان Modelsim مركـّباً على الحاسوب، فباستطاعة برنامج ISE أن يستدعي إمكانيات ModelSim لو احتاجها.

(ISE 9.2i comes with an integrated simulator)

** Limited to vendor's device-database

أمثلة:

بوابة AND:

شرح بسيط للبوابات المنطقية تقنية رقمية

تبدو كالتالي في الـ VHDL:

-- (this is a VHDL comment)

-- import std_logic from the IEEE library

library IEEE;

use IEEE.std_logic_1164.all;

-- this is the entity

entity ANDGATE is

port (

IN1 : in std_logic;

IN2 : in std_logic;

OUT1: out std_logic);

end ANDGATE;

architecture RTL of ANDGATE is

begin

OUT1 <= IN1 and IN2;

end RTL;

بينما الأمثلة في الأسفل تبدو مملة لمبتدئي VHDL فأجزاء كثيرة يمكن أن تبدو لنا اختيارية أو يمكن أن تكتب مرة واحدة فقط,بالإضافة إلى استخدام عناصر std_logic الذي يمكن استبداله بالنوع Bit ونتجنب استيراد المكتبة في البداية,لكن استخدام 9 valued logic(U,X,0,1,Z,W,L) بدلاً من (0,1) يقدم محاكاة قوية جداً وأدوات تصحيح أخطاء غير موجودة في لغات HDL الأخرى.

في الأمثلة التالية سنرى كيف أن كود VHDL يكتب بشكل مدمج لكن المصممين عادة يتجنبون النماذج المدمجة ويستخدمون أسلوب تشفير ممل أكثر من أجل أن يكون قابل للقراءة والفائدة الأخرى لاستخدام هذا الأسلوب في التشفير هي برمجة الأدوات القابلة للبرمجة مثلCPLD.

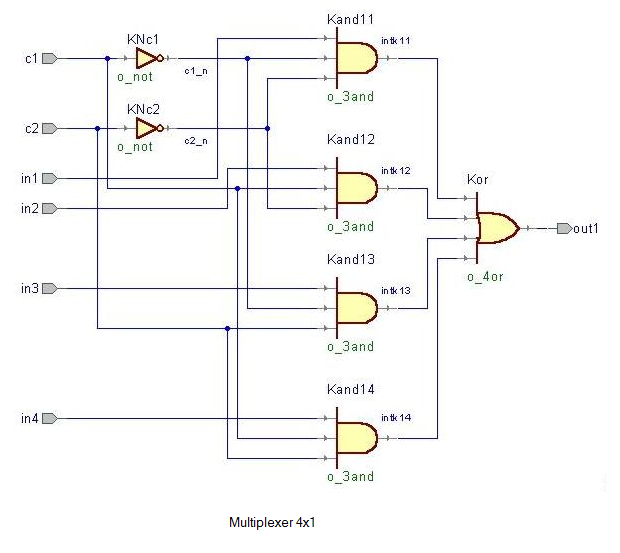

الناخب :

entity mux1b4X1 is

port(in1,in2,in3,in4,c1,c2:in Bit;out1:out Bit);

end mux1b4X1;

architecture struk_mux1b4X1 of mux1b4X1 is

signal c1_n,c2_n,intk11,intk12,intk13,intk14:Bit;

component o_not

port(in1:in Bit ;out1:out Bit);

end component ;

component o_3and is

port(in1,in2,in3:in Bit; out1:out Bit);

end component ;

component o_4or is

port(in1,in2,in3,in4:in Bit; out1:out Bit);

end component ;

begin

KNc1:o_not

port map(in1=>c1,out1=>c1_n);

KNc2:o_not

port map(in1=>c2,out1=>c2_n);

Kand11:o_3and

port map(in1=>in1,in2=>c1_n,in3=>c2_n,out1=>intk11);

Kand12:o_3and

port map(in1=>in2,in2=>c1,in3=>c2_n,out1=>intk12);

Kand13:o_3and

port map(in1=>in3,in2=>c1_n,in3=>c2,out1=>intk13);

Kand14:o_3and

port map(in1=>in4,in2=>c1,in3=>c2,out1=>intk14);

Kor:o_4or

port map(in1=>intk11,in2=>intk12,in3=>intk13,in4=>intk14,out1=>out1);

end struk_mux1b4X1;

الصورة في الأعلى تبين بنية مضمم 4×1 و بالمقبال نشاهد الشيفرة المصدرية التي يصف هذه البنية و يستخدم طريقة التوصيف البنيوي حيث نلحظ في القسم التصريحي تعداد الأجزاء التي يتكون منها المضمم (Multiplexer) و في القسم الإيعازي كيفية ارتباط تلك الأجزاء ببعضها.

أما الشيفرة المصدرية التالية فهي تصف البنية السابقة نفسها عن طريق التوصيف السلوكي.

entity mux1b4X1 is

port(in1,in2,in3,in4,c1,c2:in Bit;out1:out Bit);

end mux1b4X1;

architecture sprav_mux1b4X1 of mux1b4X1 is

begin

process(in1,in2,in3,in4,c1,c2)

begin

if c1='0' and c2='0' then

out1<=in1;

elsif c1='1' and c2='0' then

out1<=in2;

elsif c1='0' and c2='1' then

out1<=in3;

elsif c1='1' and c2='1' then

out1<=in4;

end if;

end process;

end sprav_mux1b4X1;

المغلاق :

-- latch template 1:

Q <= D when Enable = '1' else Q;

-- latch template 2:

process(D,Enable)

begin

if Enable = '1' then

Q <= D;

end if;

end process;

والمغلاق SR يستخدم إشارات التوضع والتصفير :

-- SR-latch template 1:

Q <= '1' when S = '1' else

'0' when R = '1' else Q;

-- SR-latch template 2:

process(S,R)

begin

if S = '1' then

Q <= '1';

elsif R = '1' then

Q <= '0';

end if;

end process;

والقالب المنطقي 2 يملك ضمنياً (else Q <= Q;) التي نستطيع اضافتها بصراحة إذا أردنا.

-- This one is a RS-latch (i.e. reset dominates)

process(S,R)

begin

if R = '1' then

Q <= '0';

elsif S = '1' then

Q <= '1';

end if;

end process;

قلاب المعطيات D-type flip-flops :

وهو أساس من اجل كل المنطق المتواقت

-- simplest DFF template (not recommended)

Q <= D when rising_edge(CLK);

-- recommended DFF template:

process(CLK)

begin

-- use falling_edge(CLK) to sample at the falling edge instead

if rising_edge(CLK) then

Q <= D;

end if;

end process;

-- alternative DFF template:

process

begin

wait until rising_edge(CLK);

Q <= D;

end process;

وبعض القلابات أيضاً تملك اشارات تمكين... و إشارات توضع وتصفير غير متزامنة.

-- template for asynchronous reset with clock enable:

process(CLK, RESET)

begin

if RESET = '1' then -- or '0' if RESET is active low...

Q <= '0';

elsif rising_edge(CLK) then

if Enable = '1' then -- or '0' if Enable is active low...

Q <= D;

end if;

end if;

end process;

-- template for synchronous reset with clock enable:

process(CLK)

begin

if rising_edge(CLK) then

if RESET = '1' then

Q <= '0';

elsif Enable = '1' then -- or '0' if Enable is active low...

Q <= D;

end if;

end if;

end process;

وخطأ المبتدئين الشائع أننا نملك دخل وضع وإعادة الوضع ولكن لا نستخدمها.

والمثالين التاليين غير متساويين ... الأول عبارة عن القلاب D .. والثاني عبارة عن القلاب D مع تغذية عكسية بالناخب.

-- simple D-type flip-flop

process(CLK)

begin

if rising_edge(CLK) then

Q <= D;

end if;

end process;

-- BAD VHDL: this does NOT make the flip-flop a DFF without a reset!!

process(CLK, RESET)

begin

if RESET = '1' then

-- do nothing. Q is not set here...

elsif rising_edge(CLK) then

Q <= D;

end if;

end process;

العداد:

المثال التالي عبارة عن عداد مع إعادة وضع غير متزامن ... يوضح كيفية كتابة الرنامج في الــ vhdl (كما ذكرنا سابقاً).

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all; -- for the unsigned type

entity counter_example is

generic ( WIDTH : integer := 32);

port (

CLK, RESET, LOAD : in std_logic;

DATA : in unsigned(WIDTH-1 downto 0);

Q : out unsigned(WIDTH-1 downto 0));

end entity counter_example;

architecture counter_example_a of counter_example is

signal cnt : unsigned(WIDTH-1 downto 0);

begin

Q <= cnt;

process(RESET, CLK)

begin

if RESET = '1' then

cnt <= (others => '0');

elsif rising_edge(CLK) then

if LOAD = '1' then

cnt <= DATA;

else

cnt <= cnt + 1;

end if;

end if;

end process;

end architecture counter_example_a;

سلسلة فيبوناتشي :

المثال التالي أكثر تعقيداً:

-- Fib.vhd

--

-- Fibonacci number sequence generator

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity Fibonacci is

port

(

Reset : in std_logic;

Clock : in std_logic;

Number : out unsigned(31 downto 0)

);

end entity Fibonacci;

architecture Rcingham of Fibonacci is

signal Previous : natural;

signal Current : natural;

signal Next_Fib : natural;

begin

Adder:

Next_Fib <= Current + Previous;

Registers:

process (Clock, Reset) is

begin

if Reset = '1' then

Previous <= 1;

Current <= 1;

elsif rising_edge(Clock) then

Previous <= Current;

Current <= Next_Fib;

end if;

end process Registers;

Number <= to_unsigned(Previous, 32);

end architecture Rcingham;

المصادر

[1] VHDL Primer by J.Bhasker.

طالع أيضاً

- Verilog

- SystemC

- Register transfer level

- Electronic design automation

- Complex programmable logic device (CPLD)

- Field Programmable Gate Array (FPGA)

- Application Specific Integrated Circuit (ASIC)

- Free VHDL Simulator from Xilinx [1]

وصلات خارجية

- The FAQ of news://comp.lang.vhdl

- comp.lang.vhdl Newsgroup

- IEEE VASG (VHDL Analysis and Standardization Group) - Official VHDL Working Group

- GHDL, a complete Free Software VHDL compiler/simulator, built on top of GCC.

- John's FPGA Page - List of VHDL and FPGA resources, including VHDL tutorials.

- www.opencores.org - home of many open source VHDL and Verilog projects

قراءات اضافية

- Johan Sandstrom (October 1995). "Comparing Verilog to VHDL Syntactically and Semantically". Integrated System Design. EE Times. — Sandstrom presents a table relating VHDL constructs to Verilog constructs.

- Qualis Design Corporation (2000-07-20). "VHDL quick reference card" (PDF). 1.1. Qualis Design Corporation.

- Qualis Design Corporation (2000-07-20). "1164 packages quick reference card" (PDF). 1.0. Qualis Design Corporation.

- Qualis Design Corporation (2007-03-29). "VHDL quick reference card" (PDF). 2.2. Qualis Design Corporation.

- Qualis Design Corporation (2007-03-29). "1164 packages quick reference card" (PDF). 2.2. Qualis Design Corporation.

- Janick Bergerdon, "Writing Testbenches: Functional Verification of HDL Models", 2000, ISBN 0-7923-7766-4. (The HDL Testbench Bible)